ASIC Architecture

Overline

Core Research: The ASIC Frontier

Custom Silicon for the Next Generation of Edge Intelligence

My research is driven by a singular conviction: the future of autonomous aerospace requires a fundamental shift from generic processing to specialized silicon. I focus my core research on developing proprietary ASIC architectures that are natively optimized for the unique constraints of flight-critical AI.

Micro-Architecture Optimization for AI & Redundancy

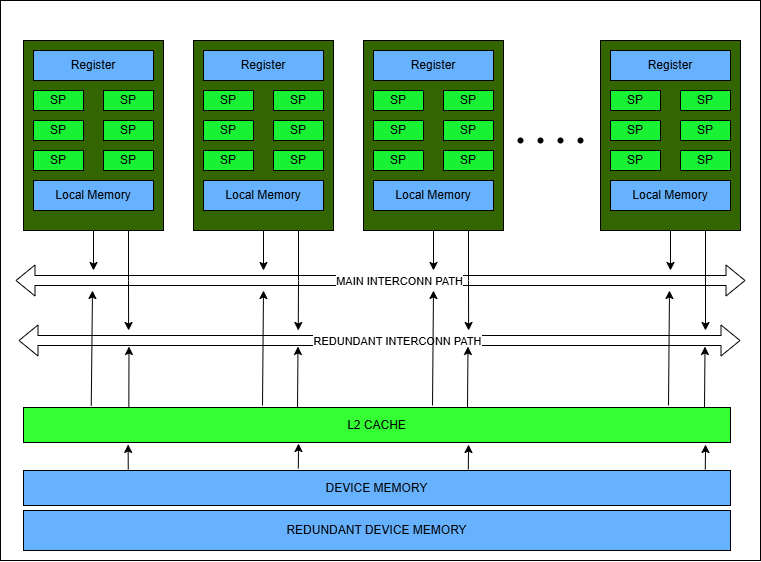

I research and develop specialized micro-architectures designed to execute neural networks at the gate level. By eliminating the overhead of general-purpose instruction sets, I create silicon paths that are specifically tuned for tensor operations. Crucially, my research integrates fault-tolerant design principles, implementing Triple Modular Redundancy (TMR) on critical functional blocks within the ASIC. This ensures that even single-event upsets or transient faults do not compromise the integrity of AI computations, making the architecture robust for safety-critical missions.

Silicon-Level Safety & Determinism

A major pillar of my research is the implementation of deterministic behavior within the silicon itself. In aerospace, ‘black box’ processing is not an option. I am investigating hardware-based monitoring circuits that can be integrated directly into the ASIC to provide real-time validation of AI outputs. This, coupled with integrated redundancy schemes, ensures that the architecture remains fully auditable and compliant with DO-254 requirements, guaranteeing predictable and safe AI decision-making

Thermal & Power Density Innovation

High-performance AI generates significant heat, a critical challenge in sealed avionics environments. My research explores the thermal boundaries of ASIC design within a scalable and modular system. I work on optimizing the physical layout of the silicon to maximize heat dissipation while accommodating the additional logic required for redundancy, allowing for unprecedented compute density without compromising the lifespan or reliability of the hardware.